За Yundong Cui, директор з технічної підтримки, Microelectronics Hercules та Mahmoud Elbanna, генеральний менеджер, Міксель-Єгипет

Нова хвиля додатків для пристроїв, що впливають на мобільні пристрої, використовуючи технологію, спочатку розроблені для мобільних пристроїв, попиту на високу роздільну здатність, потокові дані високої швидкості з датчиків зору, особливо з піднесенням моделей висновку AI, що виконують сцену в режимі реального часу та класифікацію об'єктів. Ці програми включають автомобільні, домашні автоматизації, дисплеї медичних пристроїв, нагляд та датчики IoT тощо. Природним вибором для цих конструкцій є чіпси датчика зору з MIPI® Інтерфейси, які допомагають збалансувати продуктивність із споживанням електроенергії.

Дизайнери, можливо, зможуть знаходити та вказати непереборний чіп датчика зору з MIPI, який відповідає їх вимогам пристрою, що впливає на мобільний пристрій. Однак значне рішення складається, якщо не відповідає потребам, що не відповідає чіпі. Багато з цих додатків потребують налаштування, щоб відповідати пристроям зі зниженим розміром та потужністю, що пропонує розробку спеціальної системи на мікросхемі. Можливості в цьому просторі, що впливає на мобільний, зазвичай представляє менші обсяги одиниць, що робить інвестиції в реалізації системної мікросхеми (SOC) важче обґрунтувати зі зростанням витрат на проектування та виготовлення SOC.

Відповідь на цю загадку може лежати у FPGA-не величезні, голодні силові FPGA, які сьогодні привертають більшу частину уваги, але менші, більш економічні FPGA, розроблені з пристроями, що впливають на мобільні пристрої. Ці FPGA пропонують достатню продуктивність для інтерфейсів MIPI, що працюють у високошвидкісних або низьких станах, залишаючи місце для додаткової логіки, що надається клієнтам, у відносно невеликій упаковці. У цій статті досліджуються умови, коли FPGA є надійним вибором дизайну, як виглядає реалізація MIPI у FPGA, а деякі випадки використання для дизайнерів.

Маленькі, малопотужні FPGA, що заповнюють більше ролей

Успіхи в напівпровідникових процесах зробили логіку, розміщену FPGA, набагато швидшими, ніж попередні покоління технології. Постачальники FPGA спочатку орієнтувались на ці більш швидкі пристрої на реалізацію дротового підключення на платформах класу сервера навколо таких інтерфейсів, як високошвидкісний Ethernet та PCIE. Продуктивність та щільність портів є основними критеріями дизайну в додатках, встановлених на стійках, з потужністю та охолодженням деяких проблем, але менш обмеженими, ніж у менших пристроях.

Ця швидша логіка, що розміщується FPGA, більш ніж досить швидка для інтерфейсів MIPI. Якби FPGA, яка була досить швидкою для MIPI, і споживала меншу потужність у меншому сліді, дизайнери пристроїв, що впливають на мобільний пристрій

- Швидке прототипування перед тим, як взяти на себе розвиток СОК. Ринкова життєздатність нещодавно задуманого пристрою може спиратися на підтвердження підтвердження концепції (POC), щоб забезпечити фінансування, встановити короткий список для конкурентної пропозиції або отримати відгуки клієнтів. Найкращий шлях до швидкого прототипування – це FPGA, де конструкції можуть швидко ініціювати та повторювати.

- Початкове виробництво низької швидкості або планова еволюція продукту. Вигравши першу можливість клієнта, може призвести до виробництва продукту, що базується на виробництві на основі FPGA, але в низьких обсягах одиниці, а інші взаємодії з клієнтами розвиваються. Ще однією потужною стратегією є впровадження продукту з мінімально безпечним із заздалегідь запланованими вдосконаленнями на дорожній карті, виконаній швидко з оновленнями Logic FPGA.

- Застосування з низьким обсягом у автоматизації, медичному, тестовому обладнанні та інших нішах. Деякі можливості продукту представляють тисячі одиниць замість мільйонів чи мільярдів. Ці програми з низьким обсягом часто привертають увагу комерційних позашляхових постачальників дощок та систем. Однак продукти, що не знаходяться на полиці, можуть бути складними для налаштування; Наприклад, модулі додатків розширюють можливості, але збільшують розмір, потужність та вартість. Дизайн на базі FPGA надає командам більше контролю розміру, налаштування та диференціації до середніх обсягів одиниць.

- Одинична апаратна версія з реконфігурацією. Ринки по всьому світу можуть відрізнятися за конкретними вимогами, а виробництво варіантів апаратних засобів у унікальних SKU для цільових регіонів стає складним та дорогим. Дизайн на базі FPGA може відповідати багатьом регіональним вимогам з однієї апаратної версії, при цьому FPGA переобладнана для відвантаження в кожному регіоні. Цей підхід також спрощує управління ланцюгами поставок та зменшує витрати на життєвий цикл продукту.

Оскільки додатки MIPI виникли на мобільних пристроях, дизайнери, можливо, не мали причин переглянути FPGA для інтерфейсів MIPI. Якщо дизайнери виглядають зараз, з'являється нова альтернатива.

Впровадження MIPI у FPGAS

Ці сценарії-це саме ті, які є Microelectronics Hercules, клієнтом Mixel, що дозволяє здійснювати реалізацію MIPI у двох сім'ях FPGA з низькою потужністю: HME-HME-H1D03 першого покоління та HME-H3C08 другого покоління.

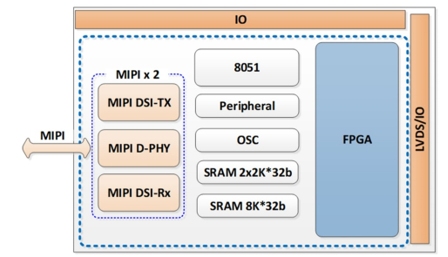

Малюнок 1: Блок-схема HME-H1D03 з Mixel Mipi D-Phy

H1D03 має 2K LUT6 блоків, що працюють на до 200 МГц, разом із інтегрованими, посиленими одноциклами 8051 ядра, SRAM та периферичними блоками та двома загартованими групами MIPI, кожна з яких має 1,5 Гбіт / с MIPI D-PHYТМ і Mipi DSI-2® Контролери TX та MIPI DSI-2 RX. Обидві групи MIPI налаштовуються на TX або RX. Підтримка дисплея становить до 2K роздільної здатності (2560×1440).

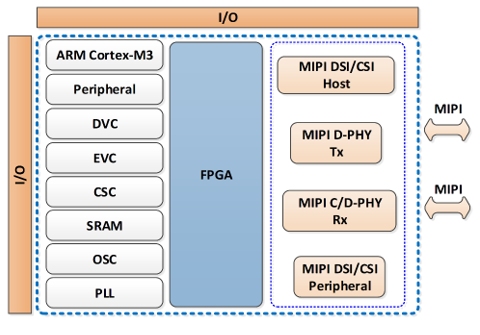

HME-H3C08 включає в себе ядро Cortex-M3 ARM, більше ніж удвічі збільшує свої блоки LUT6 до 4992, і збільшує швидкість двох загартованих 4-смугих блоків MIPI до 2,5 Гбіт / с. Він також пропонує більш широкий вибір MIPI IP для більшої гнучкості конфігурації: MIPI D-PHY та MIPI C-PHYТМ Як комбінація MIPI C-Phy/D-Phy з периферійною та CSI-2 DSI-2 та CSI-2® Контролери RX та MIPI D-Phy TX з ядрами контролера DSI-2 та CSI-2 TX.

Малюнок 2: HME H3C08 з Mixel Mipi C-Phy/D-Phy Combo та Mipi D-Phy

Затвердіння логіки MIPI у FPGA забезпечує перевірену реалізацію продукту Mipi Mipi IP, економить живлення за допомогою оптимізації та залишає істотний логічний блок FPGA безкоштовно для дизайнерського використання. Замість того, щоб мати справу з RTL для блоку MIPI та займаючись цінними LUT в програмованій логіці, дизайнери переходять безпосередньо до налаштування загартованих інтерфейсів MIPI та налаштування логіки конкретної програми для обробки потокових даних для своїх вимог пристрою. Результатом є швидший цикл проектування пристроїв, що впливає на мобільні пристрої, зберігаючи гнучкість, необхідну для диференціації продукту.

Продукти MiPI IP Mixel пропонують конфігурацію, сумісну з MIPI для досягнення різних архітектурних цілей. Два приклади-режими мосту та низької потужності.

Мости MIPI-це широкий термін, що описує можливість агрегувати, розщеплювати та післяпроцеси MIPI CSI-2 та MIPI DSI-2. Мета полягає в тому, щоб дозволити процесорам додатків-або FPGA-взаємодіяти з більш широким діапазоном дисплеїв та датчиків, включаючи конфігурації з подвійною дисплеєм або подвійним датчиком. Двоблок MIPI функція відкриває можливості мости, як ті, що показані далі.

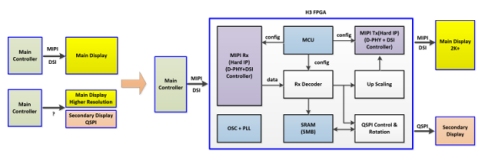

Малюнок 3: H1D03 випадки використання FPGA з низькою потужністю FPGA MIPI

Інтерфейси MIPI можуть працювати або в режимі швидкісного режиму, забезпечуючи повну роздільну здатність дисплея та частоту кадрів, або режими низької потужності, зі зниженою потужністю економії передачі даних. Координаційна роздільна здатність датчика та вибірки, швидкість кадрів та швидкість передачі MIPI, при цьому швидкий перемикання між режимами під контролем процесора застосування може збалансувати повну потокову продуктивність потоку з енергозбереженням при меншій роздільній здатності та швидкості кадру, коли це доречно. Пристрої, що впливають на мобільні пристрої, розроблені навколо цих FPGA, можуть творчо застосовувати динамічний контроль швидкості кадрів для значної економії електроенергії, зберігаючи ланцюг датчиків у режимі низької потужності для тривалої тривалості, поки не буде потрібна більш висока продуктивність.

Використовуйте випадки для MIPI у FPGAS

Включення MIPI у FPGA з малою потужністю відкриває численні випадки використання додатків для пристроїв, що впливають на мобільні пристрої. Мікроелектроніка Hercules та Mixel описують шість можливостей для різних конфігурацій.

- Підтримка дисплея вищого класу з мостом. Підтримка дисплея роздільної здатності 2K, як правило, потребує процесора додатків високого класу. FPGA може вивантажити процесор додатків низького класу за допомогою мосту MIPI, забезпечуючи функції збільшення масштабу для досягнення повної роздільної здатності.

- Ліво-правий дисплей для окулярів AR. Мікро світлодіодні дисплеї, такі як окуляри AR окуляри, використовуйте інтерфейс QSPI для зменшення кількості штифтів та розміру упаковки. FPGA може отримувати дані RGB через свій інтерфейс MIPI, розділити потік на ліво-правий компоненти та привозити підключений до QSPI мікро світлодіоди. Невеликий розмір пакету FPGA, 4,0 х 4,6 мм для H1D03 та 4,2 х 4,2 мм для H3C08, а низьке споживання електроенергії дозволяє встановити кадру.

- дисплеї EPAPER. Унікальні вимоги до сигналізації та термінів означають, що більшість процесорів додатків не розроблені для того, щоб безпосередньо керувати дисплеями EPAPER. Знову ж таки, FPGA може вивантажити завдання перетворення формату від процесора додатків і, за допомогою свого ядра мікроконтролера, може підтримувати візуальні вдосконалення, такі як алгоритми картографування кольорів.

- Розумні панелі управління домом. Більшість панелей інтелектуального дому не містять дисплеїв високої роздільної здатності, високої кадрової швидкості. Однак, як правило, вони потребують більшої периферійної інтеграції, що є ідеальним випадком використання для логіки FPGA. Дизайнери можуть додавати Wi-Fi, SD-карту, RS-232/485, сенсорний екран SPI/I2C та іншу периферійну підтримку та виконувати обробку графічних груп у FPGA, операційні автономні без процесора.

- Промислові камери. Витончені одно- або багатоспектральні датчики для промислових камер часто використовують інтерфейси LVDS, розроблені перед дебютом MIPI. Впровадження на рівні ASIC або на рівні плати в платформі управління в камері перетворює потік LVDS у стандартний інтерфейс підключення, як правило, Ethernet або USB. Ця схема може залишити виробників камер з проблемою, якщо вони хочуть перейти до нового датчика з потоковим інтерфейсом MIPI CSI-2, примушуючи відповідне оновлення дизайну платформи управління. FPGA може повернути потік MIPI CSI-2 назад до LVDS, що дозволяє оновити датчик, зберігаючи функціональність платформи управління. FPGA також може виконувати іншу попередню обробку, наприклад, відеозаписи.

- Подвійні дисплеї з головними та вторинними. Більш вдосконалений візит на ліво-правий дисплей-це націлювання на розкладні пристрої з подвійним дисплеєм, де вторинний дисплей знаходиться на зовнішньому корпусі при складанні, а головний дисплей повної роздільної здатності знаходиться всередині складки.

Клацніть, щоб збільшити

Малюнок 4: H3C08 FPGA з низькою потужністю у випадку використання подвійного дисплея

Це лише кілька прикладів, коли нова знайдена гнучкість MIPI у FPGAS надає інноваційні можливості для розробки пристроїв, що впливають на мобільний,. Оскільки датчики продовжують розмахувати від інтерфейсів LVDS до інтерфейсів MIPI CSI-2 та MIPI DSI-2, Microelectronics Hercules hme-H3C08 та HME-H1D03 та інші рішення FPGA з підтримкою MIPI, як, наприклад, виграють більше можливостей. Сценарії швидкої перевірки концепції, низької об'ємної економічної життєздатності та налаштованого апаратного забезпечення дизайнерів тягаря, ризику та витрат на складний проект SOC та завдання відшкодування витрат на розвиток за рахунок доходів від продукту. Найсучасніший MIPI IP-адреса забезпечує продуктивність, енергоефективність та потрібні дизайнери конфігурації, ставлячи їх у змогу швидше рухатися з MIPI у FPGA та досягти нових програм клієнтів.

Завітайте на веб-сайт Mixel для отримання додаткової інформації про IP-IP-кремнію Mipi, підтверджений кремнію.

Якщо ви хочете завантажити копію цієї білої книги, натисніть тут